Polyphase Clock Synchronization

5/24/24Less than 1 minute

Objective

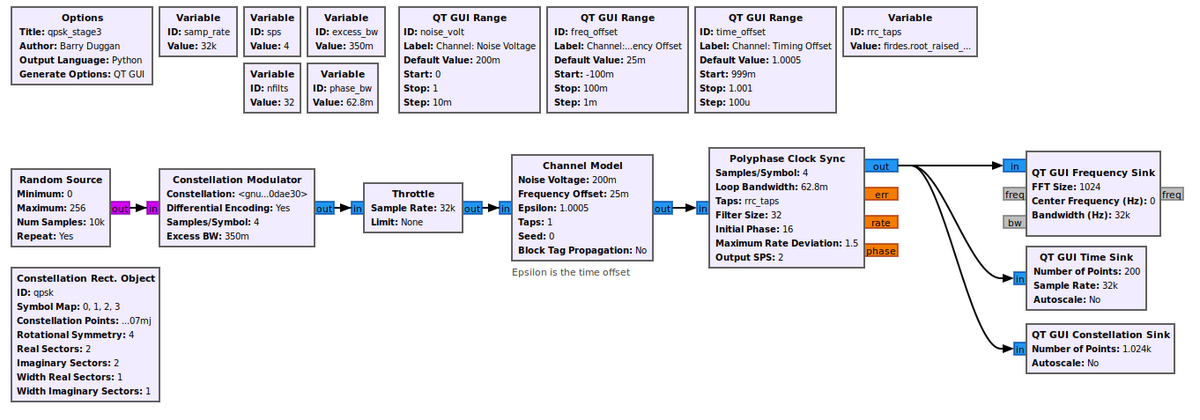

In this stage of the experiment, we will use the Polyphase Clock Sync module to implement three functions: clock recovery, inter-symbol interference (ISI) elimination, and downsampling (reducing the number of samples per symbol).

System architecture file: Qpsk_stage3.grc

Steps and Instructions

- Continuing from the previous unit, after the signal passes through the channel, use

Polyphase Clock Syncto process the received signal.- The module contains 32 filters, and the loop bandwidth is set to .

- Set the Samples per Symbol = 4.

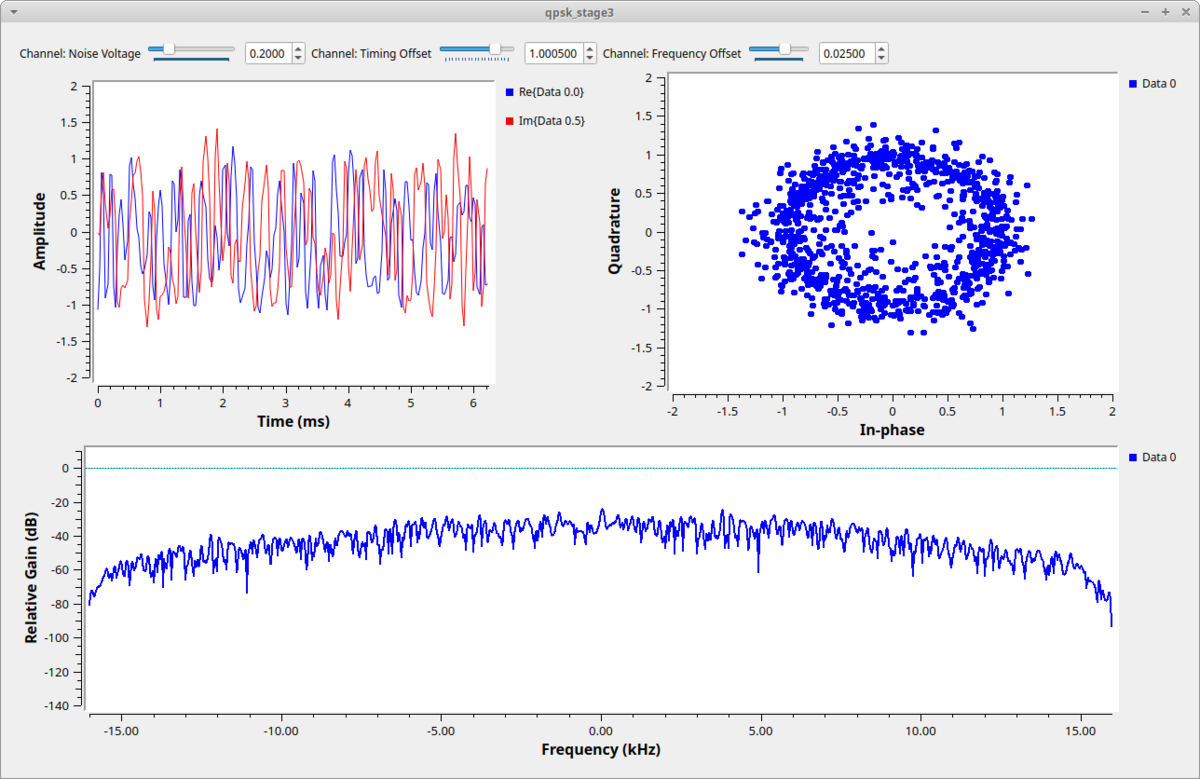

- Observe the characteristics of the time domain, frequency domain, and constellation diagram of the signal after being processed by

Polyphase Clock Sync.

System Simulation

Additional Notes

Principles of Polyphase Clock Synchronization

Clock Recovery

- Clock recovery is a crucial step in digital communication, used to determine the optimal sampling points to maximize signal power and minimize ISI.

- Polyphase clock synchronization achieves precise sampling point adjustment through multiple filters.

Matched Filter and ISI Elimination

- The Polyphase Clock Sync module incorporates a receiver-side matched filter, effectively eliminating ISI caused by the transmitter-side RRC filter.

- Through filter convolution processing, it achieves Nyquist filtering effects to reduce inter-symbol interference.

Downsampling

- The downsampling process optimizes signal processing by reducing the number of samples per symbol, thereby lowering the computational burden.

- It preserves signal integrity during processing, ensuring demodulation quality.

Exercise 4

Adjust different system parameters and compare the differences with the simulation results in the previous unit.